## 89C024XE HIGH PERFORMANCE 2400 BPS INTELLIGENT MODEM CHIP SET

- Support for Error Correction

- MNP\*\* Class 4/5

- CHMOS

- For Public Switched Telephone

Network and Unconditioned Leased

Line Applications

- V.22 bis, V.22 A/B, V.21, Bell 212A, and Bell 103 Compatible

- Serial Command Set Compatible with Hayes\* Smartmodem 2400\*

- Automatically Adapts to Remote

Modern Type with Recognition of Data

Rates

- DTMF and Pulse Dialing

- On-Chip Hybrid and Billing Delay Timer

- On-Chip Serial Port and Handshake Signals for RS-232/V.24 interface

- **■** Telephone Line Audio Monitor Output

- Analog/Digital Loopback Diagnostics with Mark/Space Pattern Generation and Error Detection

- Simple Serial Interface to External NVRAM

- Easily Customized Command Set and Features

- Two Chip Intelligent Modem Solution with Minimal External Components

- Output Programmable over 16 dB Range

- Dial and Re-dial Capability

- Full Set of Control Signals for DAA Interface

- Local, External, or Slave Timing Options in Synchronous Mode

- Adaptive Equalization

- Capable of Detecting Dial, Busy, Ringback and Modem Answer Tones of Most International Networks

- Auxiliary Relay Control Output

- Intel's MNP Software Co-Developed with R. Scott Associates\*

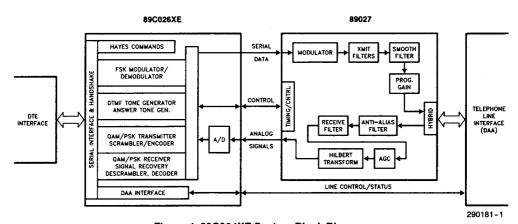

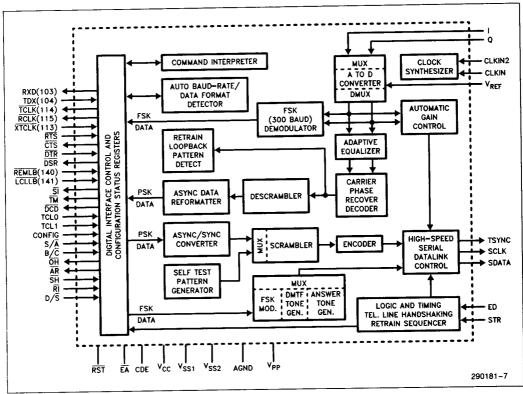

Figure 1. 89C024XE System Block Diagram

<sup>\*</sup>Hayes, Smartmodem 2400, and Smartcom II are registered trademarks of Hayes Microcomputer Products, Inc.

<sup>\*\*</sup>MNP is a registered trademark of Microcom, Inc.

R. Scott Associates, Inc., 5711 Six Forks Road, Suite 301, Raleigh, North Carolina 27609, (919) 846-7171

### **GENERAL DESCRIPTION**

Intel 89C024XE is a highly integrated, low power, high performance, intelligent modem chip set. This two chip solution is composed of the 89027 Analog Front End and 89C026XE microcontroller. At 12.96 MHz the microcontroller is capable of executing error correction and data compression routines. The system is compatible with the following CCITT and BELL standards.

- CCITT V.22 bis 2400 bps sync and async 1200 bps sync and async

- CCITT V.22 A & B 1200 bps sync and async

- CCITT V.21 0 to 300 bps anisochronous

- BELL 212A

1200 bps sync and async

300 bps fall-back mode

- BELL 103

0 to 300 bps anisochronous

The 89C024XE system consists of a 16 bit application specific processor (89C026XE) and an analog front end device (89027). The 89C026XE processor performs all "Digital Signal Processing" algorithm execution for processing the modern signals, as well as providing all modern control functions typically performed by an external processor. The analog front end provides for 2 wire and 4 wire telephone line interface, D/A conversion, and most of the complex filtering functions required in QAM/PSK/FSK moderns. Refer to Figure 1 for a simplified block diagram of the system.

In stand-alone modem applications, the 89C024XE chip set along with a Data Access Arrangement (DAA), a serial NVRAM, and RS-232 driver/receivers and EPROM with 8K x 8 static RAM represent the circuitry required for implementing an auto-dial, auto-answer, 300 to 2400 bps, MNP class 5 full duplex Hayes compatible intelligent modem.

A complete set of Industry Standard AT commands is provided for modem configuration and user interface. Virtually all PC software written for the Hayes Smartmodem 2400 can also be used with this chip set. Alternatively, in applications where user proprietary modem control commands and features are desired, the user can replace the 89C024XE command module with custom proprietary software.

The 89C024XE has a set of default features. Upon power up, the modem configuration will be in accordance with these default options, unless a different configuration has been saved in the external NVRAM with the &W command.

The 89C024XE modem has built in auto-dialing and auto-answering capabilities. It can be configured to the proper line signaling mode (Tone or Pulse), and to to the type (CCITT or Bell) and speed of the calling or answering modem. It can also detect and identify call set-up signals of telephone networks, allowing unattended data call operation.

A full set of diagnostic loop-test features compatible with CCITT V.54 is supported. The chip set also provides a line signal for audio monitoring of call progress, a comprehensive set of DAA control lines for a simple interface to the telephone network, and a full complement of TTL level RS-232/V.24 handshake signals.

#### **PACKAGING**

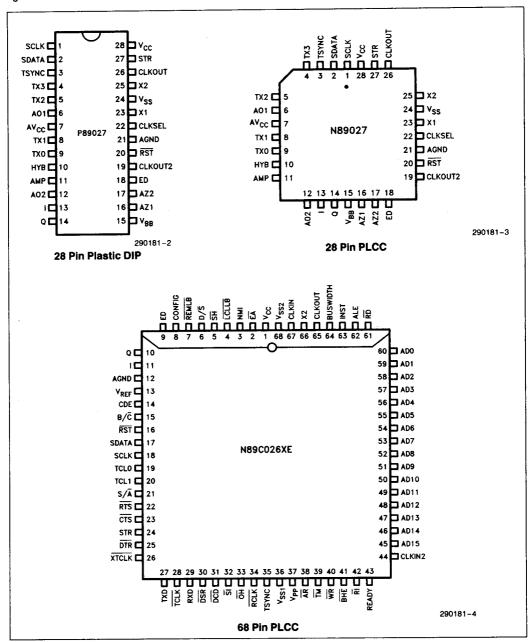

89027 is available in PLCC and standard plastic DIP packages. The 89C026XE is available in a PLCC package.

Figure 2. Device Packages

### CALL ESTABLISHMENT, TERMINATION AND RETRAIN

The 89C024XE modem system incorporates all protocols and functions required for automatic or manual call establishment. The modem system also incorporates all protocols and functions required for progress and termination of a data call.

The modem chip-set has a built-in auto-dialer, both DTMF and Pulse type. The modem can detect the dial, busy, and ringback signals at remote end, and will provide call progress messages to the user. The modem is capable of re-dialing the last number dialed, by one command.

The modern when configured for auto-answer, will answer an incoming call, remain silent for the two second billing delay interval, before transmitting the answer tones. Afterwards modern to modern identification and handshaking will proceed at a speed and operating mode acceptable to both ends of the link.

The data call can also be setup by manual dialing with the modems set to data mode, or by voice to data transfer by means of mechanical switch (exclusion key), using the  $\overline{SH}$  pin. Once set to data mode, the modem handshaking will proceed before the modems will be ready to accept and exchange data.

During data transmission, if one of the modems finds that the received data is likely to have a high bit error rate (indicated by a large mean square error in the adaptive equalizer), it initiates a retrain sequence. This automatic retrain feature is only available at 2400 bps, and is compatible with CCITT V.22 bis recommendations.

Disconnection of the data call can be initiated by the DTE at the local end or by the remote DTE, (if the modem is configured to accept it). Whether DTR will initiate a disconnect, depends on the last &D command. Receiving a long space from a remote modem will initiate a disconnect only after a Y1 command. The optional disconnect requests originated by the remote modem, are of two types, (1) disconnect when receiving long-space, and (2) disconnect when receiving long-space, and (2) disconnect.

nect when received carrier is dropped. The modem chip-set can also be configured to transmit 'long-space' just before disconnection, in each of the aforementioned cases.

Because the CCITT and Bell modem connection protocols do not provide recognition of remote modem type (i.e. V.22 bis to 212A), the Intel chip-set provides the additional capability of identifying the remote modem type. This feature is beneficial during the migration phase of the technology from the 1200 bps to 2400 bps. In North America, where the installed base of 1200 bps modems is mostly made-up of 212A type, this feature allows a "Data Base Service Provider" to easily upgrade the existing 212A modems to 2400 bps V.22 bis standard, transparently, to 212A users. Similarly, a user with a 89C024XE based modem system can automatically call data bases with either 212A or V.22 bis modems, without concern over the difference. This feature's benefits are realized in smooth upgrading of data links, with minimum cost and reduced disruption in services. Refer to Table 1 for a detailed description of remote modem compatibility.

# SOFTWARE CONFIGURATION COMMANDS

This section lists the 89C024XE commands and registers that may be used while configuring the modem. Commands instruct the modem to perform an action, the value in the associated registers determine how the commands are performed, and the result codes returned by the modem tell the user about the execution of the commands.

The commands may be entered in a string, with or without spaces in between. Any spaces within or between commands will be ignored by the modem. During the entry of any command, the 'backspace' key (CNTRL H) can be used to correct any error. Upper case or lower case characters can be used in the commands. Commands described in the following paragraphs refer to asynchronous terminals using ASCII codes.

**Table 1. Remote Modem Compatibility**

| Originating       |      |             | A            | nswering Mod | em            |               |

|-------------------|------|-------------|--------------|--------------|---------------|---------------|

| 89C024XE<br>Modem |      | Bell<br>300 | Beil<br>1200 | CCITT<br>300 | CCITT<br>1200 | CCITT<br>2400 |

| Bell              | 300  | 300         | 300          |              | 300*          | 300*          |

| Don               | 1200 | 1200*       | 1200         |              | 1200          | 1200          |

| CCITT             | 300  | _           | _            | 300          |               | _             |

| 00                | 1200 | 1200*       | 1200         | _            | 1200          | 1200          |

|                   | 2400 | 1200*       | 1200         |              | 1200          | 2400          |

| Answering         |      |             |              | Originating Mo | dem  |               |

|-------------------|------|-------------|--------------|----------------|------|---------------|

| 89C024XE<br>Modem |      | Beli<br>300 | Bell<br>1200 | CCITT<br>300   | 1200 | CCITT<br>2400 |

| Beil              | 300  | 300         | 1200         | <del></del>    | 1200 | 1200          |

| 20                | 1200 | 300         | 1200         | _              | 1200 | 1200          |

| CCITT             | 300  | _           | _            | 300            | _    | _             |

|                   | 1200 | 300*        | 1200         |                | 1200 | 1200          |

|                   | 2400 | 300*        | 1200         | _              | 1200 | 2400          |

<sup>\*</sup> These connection data rates are obtained when connecting 89C024XE based modems end to end. The same results may not be obtained when a 89C024XE based modem is connected to other modems.

#### **Command Set**

| AT   | Attention code.                         |

|------|-----------------------------------------|

| Α    | Go off-hook in answer mode              |

| Α/   | Repeat previous command string          |

| Bn   | BELL/CCITT Protocol Compatibility at    |

|      | 300 and 1200 bps                        |

| Ds   | The dialing commands                    |

|      | (0-9 A B C D * # P R T S W , ; @)       |

| En   | Echo command (En)                       |

| Hn   | Switch-Hook Control                     |

| •    | If &J1 option is selected, H1 will also |

|      | switch the auxiliary relay              |

| In   | Request Product Code and Checksum       |

| Ln   | Speaker Volume                          |

| Mn   | Monitor On/Off                          |

| 0    | On-Line                                 |

| Qn   | Result Codes                            |

| Sn=x | Write S Register                        |

| Sn?  | Read S Register                         |

| Vn   | Enable Short-Form Result Codes          |

| Xn   | Enable Extended Result Code             |

| Yn   | Enable Long Space Disconnect            |

| Z    | Fetch Configuration Profile             |

| +++  | The Default Escape Code                 |

|      |                                         |

### & Command Set (Continued)

| &C | DCD Options                                |

|----|--------------------------------------------|

| &D | DTR Options                                |

| &F | Fetch Factory Configuration Profile        |

| &G | Guard Tone                                 |

| &J | Telephone Jack Selection                   |

| &L | Leased/Dial-up Line Selection              |

| &M | Async/Sync Mode Selection                  |

| &P | Make/Break Pulse Ratio                     |

| &R | RTS/CTS Options                            |

| &S | DSR Options                                |

| &T | Test Commands                              |

| &W | Write Configuration to Non Volatile Memory |

| &X | Sync Clock Source                          |

| &Z | Store Telephone Number                     |

### **CONFIGURATION REGISTERS**

The modem stores all the configuration information in a set of registers. Some registers are dedicated to special command and function, and others are bit-mapped, with different commands sharing the register space to store the command status.

| S0*   | Ring to Answer                         |

|-------|----------------------------------------|

| S1    | Ring Count. (Read Only)                |

| S2    | Escape Code Character                  |

| S3    | Carriage Return Character              |

| S4    | Line Feed Character                    |

| S5    | Back Space Character                   |

| S6    | Wait for Dial Tone                     |

| S7    | Wait for Data Carrier                  |

| S8    | Pause Time for the Comma Dial Modifier |

| S9    | Carrier Detect Response Time           |

| S10   | Lost Carrier to Hang Up Delay          |

| S11   | DTMF Tone Duration                     |

| S12   | Escape Code Guard Time                 |

| S13   | Not Used                               |

| S14 * | Bit Mapped Option Register             |

| S15   | Not Used                               |

| S16   | Modem Test Options                     |

| S17   | Not Used                               |

| S18 * | Test Timer                             |

| S19   | Not Used                               |

| S20   | Not Used                               |

| S21 * | Bit Mapped Options Register            |

| S22 * |                                        |

| S23 * | Bit Mapped Options Register            |

| S24   | Not Used                               |

|       | Delay to DTR (Sync Only)               |

| S26 * | RTS to CTS Delay (Half Dup.)           |

| S27 * | Bit Mapped Options Register            |

#### NOTE:

#### **Dial Modifiers**

| Р  | Pulse Dial                    |

|----|-------------------------------|

| R  | Originate call in Answer Mode |

| T  | Tone Dial                     |

| S  | Dial a stored number          |

| w  | Wait for dial tone            |

| ١, | Delay a dial sequence         |

| ;  | Return to command state       |

| !  | Initiate a flash              |

#### Example:

Terminal: AT &Z T 1 (602) 555-1212

Modem: OK

Result: Modem stores T16025551212 in the ex-

ternal NVRAM.

The number can be dialed from asynchronous mode by issuing the following command:

Terminal: AT DS

Modem: T16025551212

Wait for quiet

or by turning on  $\overline{DTR}$  when in Synchronous Mode 2. Up to 33 symbols (dial digits and dial modifiers) may be stored. Spaces and other delimiters are ignored and do not need to be included in the count. If more than 33 symbols are supplied, the dial string will be truncated to 33.

### **APPLICATIONS OVERVIEW**

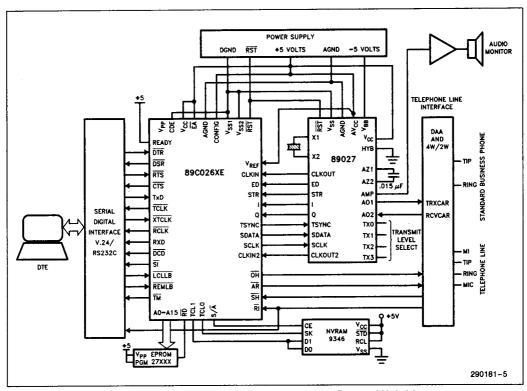

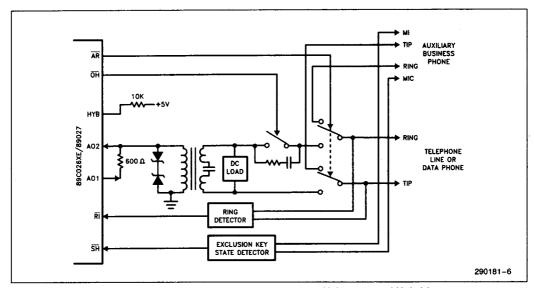

The block diagram of a stand-alone 300 to 2400 bps Hayes compatible modem is depicted in Figure 3. The DAA section shown in this diagram may be obtained with FCC registration, or implemented using the suggested diagram in Figure 4.

<sup>\*</sup> These S registers can be stored in the NVRAM.

Figure 3. Typical Modem Configuration with External Hybrid

Figure 4. Typical Telephone Line Interface Using Internal Hybrid

# SYSTEM COMPATIBILITY SPECIFICATIONS

| Parameter                                            | Specification                                                                                                                                                                               |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Synchronous                                          | 2400 bps ±0.01% V.22 bis<br>1200 bps ±0.01% V.22 and BELL 212A                                                                                                                              |  |  |  |

| Asynchronous                                         | 2400, 1200 bps, character asynchronous. 0 - 300 bps anisochronous.                                                                                                                          |  |  |  |

| Asynchronous Speed Range                             | +1% -2.5% default. Extended +2.3% -2.5% range of CCITT standards optional via software customization.                                                                                       |  |  |  |

| Asynchronous Format                                  | 10 bits, including start, stop, parity. 8, 9, 11 bits optional via S/W customization.                                                                                                       |  |  |  |

| Synchronous Timing Source                            | a) Internal, derived from the local oscillator. b) External, provided by DTE through XTCLK. c) Slave, derived from the received clock.                                                      |  |  |  |

| Telephone Line Interface                             | Two wire full duplex over public switched network or 4 wire leased lines. On-chip hybrid and billing delay timers.                                                                          |  |  |  |

| Modulation                                           | V.22 bis, 16 point QAM at 600 baud. V.22 and 212A, 4 point PSK at 600 baud. V.21 and 103, binary phase coherent FSK                                                                         |  |  |  |

| Output Spectral Shaping                              | Square root of 75% raised cosine, QAM/PSK.                                                                                                                                                  |  |  |  |

| Transmit Carrier Frequencies<br>V.22 bis, V.22, 212A | Originate 1200 Hz ± .01%<br>Answer 2400 Hz ± .01%                                                                                                                                           |  |  |  |

| V.21                                                 | Originate 'space' 1180 Hz ± .01% Originate 'mark' 980 Hz ± .01% Answer 'space' 1850 Hz ± .01% Answer 'mark' 1650 Hz ± .01%                                                                  |  |  |  |

| Bell 103 mode                                        | Originate 'space' 1070 Hz ± .01% Originate 'mark' 1270 Hz ± .01% Answer 'space' 2020 Hz ± .01% Answer 'mark' 2225 Hz ± .01%                                                                 |  |  |  |

| Receive Carrier Frequency Limits                     |                                                                                                                                                                                             |  |  |  |

| V.22 bis, V.22, 212A                                 | Originate 2400 Hz ± 7 Hz Answer 1200 Hz ± 7 Hz                                                                                                                                              |  |  |  |

| V.21                                                 | Originate 'space' 1850 Hz ± 12 Hz Originate 'mark' 1650 Hz ± 12 Hz                                                                                                                          |  |  |  |

| Bell 103                                             | Answer 'space' 1180 Hz ± 12 Hz Answer 'mark' 980 Hz ± 12 Hz Originate 'space' 2020 Hz ± 12 Hz Originate 'mark' 2225 Hz ± 12 Hz Answer 'space' 1070 Hz ± 12 Hz Answer 'mark' 1270 Hz ± 12 Hz |  |  |  |

| Typical Energy Detect Sensitivity                    | Greater than -43 dBm ED is ON. Less than -48 dBm ED is OFF. Signal in dBm measured at AO2.                                                                                                  |  |  |  |

| Energy Detect Hysteresis                             | A minimum Hysteresis of 2 dB for QAM scrambled mark.                                                                                                                                        |  |  |  |

| Line Equalization                                    | Fixed compromise equalization, transmit.  Adaptive equalizer for PSK/QAM, receive.                                                                                                          |  |  |  |

| Diagnostics Available                                | Local analog loopback.<br>Local digital loopback.<br>Remote digital loopback.                                                                                                               |  |  |  |

| Self Test Pattern Generator                          | Alternate 'ones' and 'zeros' and error detector, to be used along with most loopbacks.  A number indicating the bit errors detected is sent to DTE.                                         |  |  |  |

### **RECEIVER PERFORMANCE SPECIFICATIONS**

| Test Cases     |                   | Typical SNR for<br>10 <sup>-5</sup> BER Performance |                |  |

|----------------|-------------------|-----------------------------------------------------|----------------|--|

| Data<br>Mode   | Rx Level<br>(dBm) | Answer<br>(dB)                                      | Originate (dB) |  |

| V.22 bis       | -30               | 16                                                  | 16.5           |  |

| Synchronous    | -40               | 16.5                                                | 18             |  |

| V.22/Bell 212A | -30               | 6.5                                                 | 6.5            |  |

| Synchronous    | -40               | 6.5                                                 | 6.5            |  |

| V.21           | -30               | 9                                                   | 7.5            |  |

| Asynchronous   | -40               | 9                                                   | 8              |  |

| Bell 103       | -30               | 10                                                  | 11.5           |  |

| Asynchronous   | -40               | 10                                                  | 11.5           |  |

#### Test Conditions:

- Receive Signal (Rx) measured at A02 (transmit level set at −9 dBm)

- Unconditioned 3002 Line

- 3 KHz Flat-Band Noise

### PERFORMANCE SPECIFICATIONS

| Parameter                                   | Min  | Тур            | Max | Units    | Comments                                |

|---------------------------------------------|------|----------------|-----|----------|-----------------------------------------|

| DTMF Level                                  |      | 4.0            |     | dBm      | at AO1                                  |

| DTMF Second Harmonic                        |      |                | -35 | dB       | HYB enabled into $600\Omega$            |

| DTMF Twist (Balance)                        |      | 3              |     | dB       |                                         |

| Default DTMF Duration                       |      | 100            |     | ms       | Software Controlled                     |

| Pulse Dialing Rate                          |      | 10             |     | pps      |                                         |

| Pulse Dialing Make/Break                    |      | 39/61<br>33/67 |     | %<br>%   | US<br>UK, Hong Kong                     |

| Pulse Interdigit Interval                   |      | 785            |     | ms       |                                         |

| Billing Delay Interval                      |      |                | 2.1 | sec      |                                         |

| Guard Tone Frequency<br>Amplitude           |      | 540<br>-3      |     | Hz<br>dB | referenced to High<br>Channel transmit. |

| Frequency<br>Amplitude                      |      | 1800<br>-6     |     | Hz<br>dB | QAM/PSK Modes Only                      |

| Dial Tone Detect Duration                   |      | 3.0            |     | sec      |                                         |

| Ringback Tone Detect<br>Duration<br>Cadence |      | 0.75<br>1.5    |     | sec      | Off/On Ratio                            |

| Busy Tone Detect<br>Duration<br>Cadence     | 0.67 | 0.2            | 1.5 | sec      | Off/On Ratio                            |

### 89C026XE OVERVIEW

The 89C026XE processor performs data manipulation, signal processing and user interface functions. It supports external ROM and RAM to perform asynchronous, synchronous, and/or custom code with or without high level protocol functions. These options will allow proprietary modem control, functions, call progress management applications to be implemented. A block diagram of the 89C026XE is provided in Figure 5.

89C026XE contains a TTL compatible serial link to DTE equipment, along with a full complement of V.24/RS-232-C control signals. Alternatively, a UART or USART may be used directly to transfer data to and from a microcomputer bus. The industry standard AT command set is supported by the 89C026XE, facilitating compatability between 89C024XE and most PC software written for the AT command set.

During transmit operation, the 89C026XE synthesizes DTMF tones and the 300 BPS FSK modem

signal and transmits them to the 89027 as digitized amplitude samples. During 1200 and 2400 BPS operation, DPSK and QAM is used to send 2 to 4 bits of information respectively at 600 baud to the AFE. Because the QAM coding technique is an inherently synchronous transmission mechanism, in the case of asynchronous QAM transmission, the asynchronous data is synchronized by adding or deleting stop bits. Following the synchronization process, the 89C026XE transmits digitized phase and amplitude samples to 89027 over the high speed serial link.

In the receive operation, the information is received by the 89C026XE from the 89027 as two signals which are 90 degrees phase shifted from each other. These analog signals are then digitized by the A/D converter resident on the 89C026XE. By using DSP algorithms, the received signals are processed using adaptive equalization for telephone line delay, amplitude distortion and gain adjustment is executed and the signal demodulated. Following demodulation, the data is unscrambled, and if necessary, returned to asynchronous format.

Figure 5. 89C026XE Block Diagram

### 89C026XE PINOUT

| Symbol           | Function (89C024XE)                                       | Direction | Pin No. |

|------------------|-----------------------------------------------------------|-----------|---------|

| CLKIN            | 12.96 MHz master clock from 89027                         | In        | 67      |

| CLKIN2           | 270 KHz from 89027                                        | In        | 44      |

| RST              | Chip reset (active low)                                   | ln        | 16      |

| -                | In-phase received signal                                  | In        | 11      |

| Q                | Quadrature-phase received signal                          | ln        | 10      |

| STR              | Symbol Timing from 89027                                  | ln        | 24      |

| ED               | Energy Detect input                                       | ln .      | 9       |

| TSYNC            | Transmitter sync pulse to 89027                           | Out       | 35      |

| SDATA            | Serial Data to 89027                                      | Out       | 17      |

| SCLK             | Serial Clock to 89027                                     | Oút       | 18      |

| OH               | Off-Hook control to DAA                                   | Out       | 33      |

| SH               | Switch-Hook from dataphone                                | In        | 5       |

| RΪ               | Ring Indicator from DAA                                   | In        | 42      |

| ĀR               | Aux Relay control to DAA                                  | Out       | 38      |

| TCL1             | NVRAM Data I/O                                            | 1/0       | 20      |

| TCL0             | NVRAM CLK                                                 | Out       | 19      |

| B/ <del>C</del>  | Reserved for future use (V <sub>CC</sub> )(3)             | In        | 15      |

| S/Ā              | NVRAM CE                                                  | Out       | 21      |

| D/S              | Dumb/Smart mode select                                    | In        | 6       |

| CONFIG           | Reserved for future use (V <sub>CC</sub> ) <sup>(3)</sup> | In        | 8       |

| TM               | Test Mode Indicator                                       | Out       | 39      |

| TXD              | Transmitted data from DTE                                 | In        | 27      |

| RXD              | Received data to DTE                                      | Out       | 29      |

| RTS              | Request to send from DTE                                  | ln        | 22      |

| CTS              | Clear to Send to DTE                                      | Out       | 23      |

| DSR              | Data Set Ready to DTE                                     | Out       | 30      |

| DCD              | Data Carrier Detect to DTE                                | Out       | 31      |

| DTR              | Data Terminal Ready from DTE                              | ln        | 25      |

| RCLK             | Received clock to DTE                                     | Out       | 34      |

| TCLK             | Transmit clock to DTE                                     | Out       | 28      |

| XTCLK            | External timing clock from DTE                            | In        | 26      |

| SI               | Speed Indicator to DTE                                    | Out       | 32      |

| REMLB            | Remote Loopback Command from DTE                          | ln ln     | 7       |

| LCLLB            | Local Loopback Command from DTE                           | In        | 4       |

| V <sub>CC</sub>  | Positive power supply (+5V)                               | +5V       | 1       |

| CDE              | Clock detect enable (V <sub>SS</sub> ) <sup>(1)</sup>     | GND       | 14      |

| VREF             | A/D converter reference                                   | +5V       | 13      |

| V <sub>SS1</sub> | Digital ground                                            | GND       | 36      |

| $V_{SS2}$        | Digital ground                                            | GND       | 68      |

| AGND             | Analog ground                                             | AGND      | 12      |

| V <sub>PP</sub>  | (NC) <sup>(2)</sup>                                       | In        | 37      |

| ĒĀ               | External Memory enable                                    | ln .      | 2       |

| AD0-AD15         | External memory access address/data <sup>(4)</sup>        | 1/0       | 60-45   |

| ĀĀ               | Auto Answer <sup>(4)</sup>                                | Out       | 60      |

| <u>JS</u>        | Jack Select <sup>(4)</sup>                                | Out       | 59      |

| <u>CD</u>        | Carrier Detect Indicator <sup>(4)</sup>                   | Out       | 58      |

| MR               | Modem Ready Indicator <sup>(4)</sup>                      | Out       | 57      |

#### 89C026XE PINOUT (Continued)

| Symbol   | Function (89C026XE)                                    | Direction | Pin No. |

|----------|--------------------------------------------------------|-----------|---------|

|          | No-maskable Interrupt(V <sub>SS</sub> ) <sup>(1)</sup> | in        | 3       |

| NMI      | Crystal output(NC) <sup>(2)</sup>                      | Out       | 66      |

| X2       | l .                                                    | Out       | 65      |

| CLKOUT   | Clk output                                             | in        | 64      |

| BUSWIDTH | Bus Width                                              | Out       | 63      |

| INST     | External memory instruction fetch                      |           | 62      |

| ALE      | Address latch enable                                   | Out       | 61      |

| RD       | External memory read                                   | Out       | 1       |

| READY    | External memory ready                                  | l In      | 43      |

| BHE      | External memory bus high enable                        | Out       | 41      |

| WR       | External memory write                                  | Out       | 40      |

#### NOTES:

- 1. Pins marked with (VSS) must be connected to VSS.

- 2. Pins marked with (NC) are to be left unconnected.

- 3. Pins marked with (V<sub>CC</sub>) must be connected to V<sub>CC</sub>.

- 4. With internal ROM enabled, AD0-AD3 are used as AA, JS, CD, and MR respectively.

- 5. Pins with direction "IN" must not be left floating.

### 89C026XE PIN DESCRIPTION

#### **XTCLK**

Transmitter timing from DTE, when external clock option is selected.

#### TXD

The serial data from DTE to be transmitted on the line. A logic 'high' is mark. In synchronous mode, 89026 samples this data on the rising edges of TCLK.

#### TCLK

Clock output from 89026 as timing source for data exchange from DTE to modem. Serial data is read on the rising edges of the TCLK. This output is High in asynchronous mode.

#### RXD

The serial data to DTE. 'Mark' is a logic High. In synchronous mode, the rising edge of RCLK occurs in the middle of RXD.

#### RCLK

Synchronous clock output. Rising edge of RCLK occurs in the middle of each RXD bit. This pin remains High in asynchronous mode.

#### Vpp

This function is not used and should not be connected.

#### TM

A Low indicates maintenance condition in the modem.

#### DCD

In async operation, DCD remains Low regardless of data carrier (default), or it can be programmed to indicate received carrier signal is within the required timing and amplitude limits. In sync operation Low indicates the received carrier signal is within the required timing and amplitude limits.

#### DSR

Low indicates modem is off-hook, and it is in data transmission mode, and the answer tone is being exchanged. CTS Low indicates modem is prepared to accept data.

#### RTS

In async mode RTS is ignored. Under command control, in sync mode RTS can be ignored, or the modem can respond with a Low on CTS.

#### DTR

&D0 command will cause the modem to ignore DTR. For &D1 the modem assumes the asynchronous command state on a Low to High transition of the DTR circuit. The &D2 command does the same as &D1 except the state of DTR will enable/disable auto answer. A Low to High transition of DTR after the &D3 command will cause the modem to assume the initialization state.

#### TCL1, TCL0

These pins are used as the serial clock and data for interface to an NVRAM. Refer to Figure 3. TCL0 is used to output a clock and serial data is transferred in on TCL1.

#### AR

This Auxiliary relay control is for switching a relay for voice or data calls. High is voice, Low is data.

#### RI

A Low signal from DAA indicates line ringing. This input is ignored when the modern is configured for leased line. This signal should follow the ring cadence.

#### OH

Low sets an off hook condition, high indicates an on hook. When dialing, this signal is used to pulse dial the line.

#### $\overline{SH}$

Used as a telephone voice to data switch or vice versa. Any logic level transition will toggle the modern state. This input is ignored, if a software command attempts to switch the modern between voice and data.

#### ĀĀ

Used as an indicator for Auto Answer status and Ring indicator. Active low.

#### LCLLB

A Low will set the modem in the local analog loop-back test mode. Logic Low levels applied simultaneously to REMLB and LCLLB pins, sets the modem to the local digital loopback.

#### REMLB

A logic Low on this pin initiates a remote loopback condition.

#### CD

A Low indicates the presence of carrier signal on the line.

#### MR

A Low indicates the presence of the DSR signal. Toggling indicates that a test mode is active.

#### SI

Selects one of the two data rates or ranges of rates in the DTE to correspond to the rate in modem. Low selects the higher rate (2400 CCITT/1200 BELL) or range of rates. High selects the Low rate or range of rates.

#### D/S

A Low on this pin will indicate the smart mode which will respond to all commands. A High will ignore all commands.

#### VREF

Voltage reference for the analog to digital converter should be connected to the 89027 AVcc.

#### CDE

This pin must be connected to VSS.

#### S/Ā

The function of this pin is re-defined as external NVRAM CE.

#### CONFIG

Reserved for future use. This signal should be pulled high.

#### EA

When high, memory access from address 2000H to 4000H are directed to on-chip ROM. When low, all Memory access is directed to off-chip memory.

#### JS

Low is used to pulse A and A1 leads to control a 1A2 Key System jack.

#### **BUSWIDTH**

When high, external memory accesses are 16 bits wide. When low, external memory accesses are 8 bits wide.

#### READY

When high, no wait states are inserted in external memory accesses. When low, one wait state is inserted in each external memory access.

### 89C026XE ABSOLUTE MAXIMUM **RATINGS\***

| Temperature Under Bias0°C to +70°C                           |

|--------------------------------------------------------------|

| Storage Temperature40°C to +125°C                            |

| Voltage from Any Pin to V <sub>ss</sub> or AGND0.5V to +7.0V |

| Average Output Current from Any Pin10 mA                     |

| Power Dissipation                                            |

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTICE: Specifications contained within the following tables are subject to change.

### **OPERATING CONDITIONS**

| Symbol           | Parameter                      | Min      | Max      | Units |  |

|------------------|--------------------------------|----------|----------|-------|--|

| TA               | Ambient Temperature Under Bias | 0        | + 70     | °C    |  |

| V <sub>CC</sub>  | Digital Supply Voltage         | 4.75     | 5.25     | V     |  |

| V <sub>REF</sub> | Analog Supply Voltage          | 4.75     | 5.25     | V     |  |

| fosc             | CLKIN Frequency                | 12.95870 | 12.96130 | MHz   |  |

#### NOTE:

The AGND and VSS on both the 89C026XE and the 89027 must be nominally at the same potential.

### DC CHARACTERISTICS

| Symbol           | Parameter                                                                            | Min                                                                     | Typ(7) | Max                   | Units                 | Test Conditions                                                                                              |

|------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------|-----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                                                    | -0.5                                                                    |        | + 0.8                 | ٧                     |                                                                                                              |

| V <sub>IH</sub>  | Input High Voltage(1)                                                                | 0.2 V <sub>CC</sub> + 0.9                                               |        | V <sub>CC</sub> + 0.5 | ٧                     |                                                                                                              |

| V <sub>IH1</sub> | Input High Voltage on CLKIN                                                          | 0.7 V <sub>CC</sub>                                                     |        | V <sub>CC</sub> + 0.5 | V                     |                                                                                                              |

| V <sub>IH2</sub> | Input High Voltage on RESET                                                          | 2.2                                                                     |        | V <sub>CC</sub> + 0.5 | V                     |                                                                                                              |

| V <sub>OL</sub>  | Output Low Voltage                                                                   |                                                                         |        | 0.3<br>0.45<br>1.5    | \                     | $I_{OL}=200~\mu A$<br>$I_{OL}=3.2~m A$<br>$I_{OL}=7~m A$                                                     |

| V <sub>OH</sub>  | Output High Voltage <sup>(4)</sup>                                                   | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |        |                       | <b>&gt; &gt; &gt;</b> | $\begin{split} I_{OH} &= -200~\mu\text{A} \\ I_{OH} &= -3.2~\text{mA} \\ I_{OH} &= -7~\text{mA} \end{split}$ |

| V <sub>OH1</sub> | Output High Voltage <sup>(3)</sup>                                                   | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |        |                       | V<br>V                | $I_{OH} = -10 \mu A$ $I_{OH} = -30 \mu A$ $I_{OH} = -60 \mu A$                                               |

| ILI              | Input Leakage Current(5)                                                             |                                                                         |        | ±10                   | μΑ                    | $0 < V_{IN} < V_{CC} - 0.3V$                                                                                 |

| I <sub>LI1</sub> | Input Leakage Current(6)                                                             |                                                                         |        | ±3                    | μΑ                    | 0 < V <sub>IN</sub> < V <sub>REF</sub>                                                                       |

| I <sub>IL</sub>  | Logical 0 Input Current(3)                                                           |                                                                         |        | -50                   | μΑ                    | V <sub>IN</sub> = 0.45V                                                                                      |

| I <sub>IL1</sub> | Logical 0 Input Current<br>in RESET <sup>(2)</sup> (ALE, RD,<br>WR, BHE, INST, SCLK) |                                                                         |        | -850                  | μΑ                    | V <sub>IN</sub> = 0.45V                                                                                      |

### DC CHARACTERISTICS (Continued)

| Symbol           | Parameter                                        | Min | Typ(7) | Max | Units | Test Conditions                                                                                                                               |

|------------------|--------------------------------------------------|-----|--------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>REF</sub> | A/D Converter Reference Current                  |     | 2      | 5   | mA    | $\begin{array}{c} \text{CLKIN} = 12.96 \text{ MHz} \\ \text{V}_{\text{CC}} = \text{V}_{\text{PP}} = \text{V}_{\text{REF}} = 5.25 \end{array}$ |

| I <sub>CC1</sub> | Active Mode Current (Typical)                    |     | 45     | 60  | mA    | CLKIN = 12.96 MHz                                                                                                                             |

| R <sub>RST</sub> | RESET Pullup Resistor                            | 6K  |        | 50K | Ω     |                                                                                                                                               |

| Cs               | Pin Capacitance<br>(Any Pin to V <sub>SS</sub> ) |     |        | 10  | pF    | f <sub>TEST</sub> = 1.0 MHz                                                                                                                   |

#### NOTES:

(Notes apply to all specifications)

1. All pins except RESET and CLKIN.

- 2. Holding these pins below V<sub>IH</sub> in RESET may cause the part to enter test modes. 3. TCL0, TCL1, S/Ā, RTS, CTS, DSR, DCD, SI, OH.

- 4. BHE, INST, CLKOUT, RESET, TCLK, RXD, RCLK, TSYNC, TM, SCLK, SDATA. The VOH specification is not valid for RESET.

- 5. CDE, EA, READY, BUSWIDTH, NMI, STR, DTR, XTCLK, TXD, B/C, CLKIN2, and RI.

- 6. S/D, SH, REMLB, LCLLB, I, Q, CONFIG, ED.

- 7. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and  $V_{REF} = V_{CC} = 5V$ .

## A.C. CHARACTERISTICS (Over specified operating conditions)

Test Conditions: Capacitive load on all pins = 100 pF, Rise and fall times = 10 ns, f<sub>OSC</sub> 12.96 MHz

### This system must meet these specifications to work with 89C026XE:

| Symbol            | Parameter                         | Min                   | Max                     | Units | Notes    |

|-------------------|-----------------------------------|-----------------------|-------------------------|-------|----------|

| TAVYV             | Address Valid to READY Setup      |                       | 2T <sub>OSC</sub> - 85  | ns    |          |

| T <sub>LLYV</sub> | ALE Low to READY Setup            |                       | T <sub>OSC</sub> - 72   | ns    |          |

| T <sub>YLYH</sub> | Non READY Time                    | No Up                 | per Limit               | ns    |          |

| T <sub>CLYX</sub> | READY Hold after CLKOUT Low       | 0                     | T <sub>OSC</sub> - 30   | ns    | (Note 1) |

| TLLYX             | READY Hold after ALE Low          | T <sub>OSC</sub> - 15 | 2 T <sub>OSC</sub> - 40 | ns    | (Note 1) |

| TAVGV             | Address Valid to Buswidth Setup   | -                     | 2 T <sub>OSC</sub> - 85 | ns    |          |

| TLLGV             | ALE Low to Buswidth Setup         |                       | T <sub>OSC</sub> - 70   | ns    |          |

| TCLGX             | Buswidth Hold after CLKOUT Low    | 0                     | ·                       | ns    |          |

| TAVDV             | Address Valid to Input Data Valid |                       | 3 T <sub>OSC</sub> - 67 | ns    |          |

| T <sub>RLDV</sub> | RD Active to Input Data Valid     |                       | T <sub>OSC</sub> - 23   | ns    | <u> </u> |

| TCLDV             | CLKOUT Low to Input Data Valid    |                       | T <sub>OSC</sub> - 50   | ns    |          |

| TRHDZ             | End of RD to Input Data Float     |                       | T <sub>OSC</sub> - 20   | ns    |          |

| TRXDX             | Data Hold after RD Inactive       | 0                     |                         | ns    |          |

<sup>1.</sup> If max is exceeded, additional wait states will occur.

### A.C. CHARACTERISTICS (Continued)

Test Conditions: Capacitive load on all pins = 100 pF, Rise and fall tines = 10 ns, f<sub>OSC</sub> 12.96 MHz

#### The 89C026XE will meet these specifications:

| Symbol             | Parameter                                     | Min                       | Max                       | Units | Notes    |

|--------------------|-----------------------------------------------|---------------------------|---------------------------|-------|----------|

| F <sub>CLKIN</sub> | Oscillator Frequency                          | 12.95870                  | 12.96130                  | MHz   |          |

| Tosc               | Oscillator Period                             | 1/F <sub>CLKIN(MAX)</sub> | 1/F <sub>CLKIN(MIN)</sub> | ns    |          |

| T <sub>XHCH</sub>  | F <sub>CLKIN</sub> High to CLKOUT High or Low | 40                        | 110                       | ns    | (Note 1) |

| TCLCL              | CLKOUT Cycle Time                             | 2 T <sub>0</sub>          | osc                       | ns    |          |

| T <sub>CHCL</sub>  | CLKOUT High Period                            | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 10     | ns    |          |

| T <sub>CLLH</sub>  | CLKOUT Falling Edge to ALE Rising             | -5                        | 15                        | ns    |          |

| T <sub>LLCH</sub>  | ALE Falling Edge to CLKOUT Rising             | -15                       | 15                        | ns    |          |

| T <sub>LHLH</sub>  | ALE Cycle Time                                | 4 T <sub>0</sub>          | osc                       | ns    |          |

| T <sub>LHLL</sub>  | ALE High Period                               | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 10     | ns    |          |

| TAVLL              | Address Setup to ALE Falling Edge             | T <sub>OSC</sub> - 20     |                           | ns    |          |

| TLLAX              | Address Hold after ALE Falling Edge           | T <sub>OSC</sub> - 40     |                           | ns    |          |

| T <sub>LLRL</sub>  | ALE Falling Edge to RD Falling Edge           | T <sub>OSC</sub> - 40     |                           | ns    |          |

| TRLCL              | RD Low to CLKOUT Falling Edge                 | 5                         | 30                        | ns    |          |

| T <sub>RLRH</sub>  | RD Low Period                                 | T <sub>OSC</sub> - 5      | T <sub>OSC</sub> + 25     | ns    |          |

| TRHLH              | RD Rising Edge to ALE Rising Edge             | Tosc                      | T <sub>OSC</sub> + 25     | ns    | (Note 2) |

| T <sub>RLAZ</sub>  | RD Low to Address Float                       |                           | 10                        | ns    |          |

| T <sub>LLWL</sub>  | ALE Falling Edge to WR Falling Edge           | T <sub>OSC</sub> - 10     |                           | ns    |          |

| T <sub>CLWL</sub>  | CLKOUT Low to WR Falling Edge                 | 0                         | 25                        | ns    |          |

| TQVWH              | Data Stable to WR Rising Edge                 | T <sub>OSC</sub> - 23     |                           | ns    |          |

| T <sub>CHWH</sub>  | CLKOUT High to WR Rising Edge                 | -10                       | 10                        | ns    |          |

| T <sub>WLWH</sub>  | WR Low Period                                 | T <sub>OSC</sub> - 30     | Tosc + 5                  | ns    |          |

| T <sub>WHQX</sub>  | Data Hold after WR Rising Edge                | T <sub>OSC</sub> - 10     |                           | ns    |          |

| T <sub>WHLH</sub>  | WR Rising Edge to ALE Rising Edge             | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 15     | ns    | (Note 2) |

| T <sub>WHBX</sub>  | BHE, INST HOLD after WR Rising Edge           | T <sub>OSC</sub> 10       |                           | ns    |          |

Typical specifications, not guaranteed.

Assuming back-to-back bus cycles.

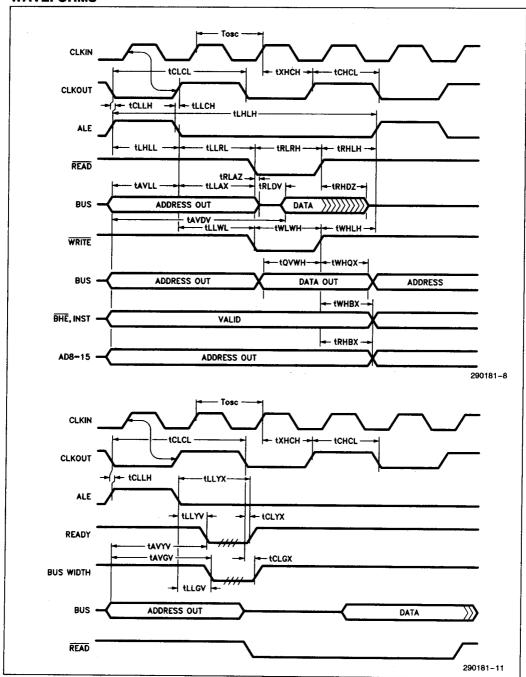

#### **WAVEFORMS**

Figure 6. Bus Signal Timings

#### 89027 OVERVIEW

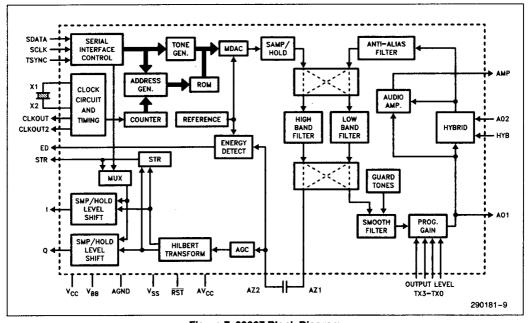

The 89027 is a 28 pin CHMOS analog front end device, which performs most of the complex filtering functions required in modern transmitters and receivers. A general block diagram of this chip is provided in Figure 7. Most of the analog signal processing functions in this chip are implemented with CHMOS switched capacitor technology. The 89027 functions are controlled by 89C026XE, through a high speed serial data link.

During FSK transmit operation, the 89027 receives digitally synthesized mark and space sinusoid amplitude information from the 89C026XE. The 89027 converts the signal to its analog equivalent, filters it, and transmits it to the telephone line. For QAM transmission, the signal constellation points are transferred to the 89027. This information is modulated into an analog signal, passed through spectral

shaping filters, combined with the necessary guard tone, smoothed by a low pass filter, and transmitted to the line. Prior to transmitting either FSK or QAM signals to the telephone line, the 89027 adjusts the signal gain through an on-board programmable gain amplifier.

During the receive operation, the received FSK and QAM signals are passed through anti-alias filters, bandsplit filters, automatic gain control and carrier detect circuits, a Hilbert transform filter, and the output sent to the 89C026XE processor as analog signals.

Other functions provided by the 89027 are: an onboard two wire to four wire circuit with disable capability, an audio monitor output with software configurable gain, and a programmable gain transmit signal.

The 89027 is available in 28 pin plastic DIP and PLCC packages.

Figure 7. 89027 Block Diagram

### **89027 PINOUT**

| Symbol             | Function (89027)                             | Direction | Pin No. |

|--------------------|----------------------------------------------|-----------|---------|

| V <sub>CC</sub>    | Positive Power Supply (Digital)              | + 5V      | 28      |

| $V_{BB}$           | Negative Power Supply                        | -5V       | 15      |

| $V_{SS}$           | Digital Ground                               | DGND      | 24      |

| AGND               | Analog Ground                                | AGND      | 21      |

| AV <sub>CC</sub> - | Positive Power Supply (Analog)               | +5        | 7       |

| X1                 | Xtal Oscillator                              | in        | 23      |

| X2                 | Xtal Oscillator                              | Out       | 25      |

| CLKOUT             | 12.96 MHz Clock Output to 89C026XE           | Out       | 26      |

| CLKOUT2            | 270 KHz Clock Output to 89C026XE             | Out       | 19      |

| RST                | Chip reset (active low)(1)                   | In        | 20      |

| HYB                | Enable on-chip hybrid <sup>(1)</sup>         | ln        | 10      |

| AZ1                | Auto-zero capacitor                          | Out       | 16      |

| AZ2                | Auto-zero capacitor                          | In        | 17      |

| SDATA              | Serial data from 89C026XE                    | In        | 2       |

| SCLK               | Serial clock from 89C026XE                   | In        | 1       |

| TSYNC              | Transmitter sync from 89C026XE               | In        | 3       |

| STR                | Symbol timing to 89C026XE                    | Out       | 27      |

| ED                 | Receiver energy detect to 89C026XE           | Out       | 18      |

| 1                  | In phase received signal to 89C026XE         | Out       | 13      |

| Q                  | Quadrature-phase received signal to 89C026XE | Out       | 14      |

| AO1                | Transmitter output                           | Out       | 6       |

| AO2                | Receiver input                               | In        | 12      |

| AMP                | Output to monitor speaker                    | Out       | 11      |

| TX0                | Transmitter level control (LSB)(1)           | In        | 9       |

| TX1                | Transmitter level control(1)                 | in        | 8       |

| TX2                | Transmitter level control(1)                 | in in     | 5       |

| TX3                | Transmitter level control (MSB)(1)           | ln in     | 4       |

| NC                 | (Note 2)                                     | In        | 22      |

#### NOTE:

1. When held high, these pins must be connected through 10K resistors to V<sub>CC</sub>.

2. Reserved Pin. Must be left No Connect.

### 89027 Pinout Description

#### TX0-3

These four pins control the transmitted signal level. Refer to Transmit Level Table.

#### HYB

This pin enables the on-chip hybrid. A line impedance matching network must be connected between AO1 and AO2 when HYB is enabled. If HYB is disabled and an external 4W/2W hybrid is used, the hybrid receive path must be amplified by 6 dB.

#### A01

Transmitter output.

#### **AO2**

Receiver input.

#### AMP

This output can be used to monitor the call progress tones and operation of the line.

## ABSOLUTE MAXIMUM RATINGS(2)

| Temperature Under Bias 0 to +70° C                                                                  |

|-----------------------------------------------------------------------------------------------------|

| Storage Temperature40 to +125° C                                                                    |

| All Input and Output Voltages with Respect to V <sub>BB</sub> 0.3V to +13.0V                        |

| All Input and Output Voltages with Respect to V <sub>CC</sub> & AV <sub>CC</sub> $-13.0V$ to $0.3V$ |

| Power Dissipation1.35W                                                                              |

| Voltage with Respect to Vec(1)                                                                      |

#### NOTES:

1. Applies to pins SCLK, SDATA, TSYNC, RST, HYB, TX0-TX3 only.

2. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# POWER DISSIPATION Ambient Temp = 0° to 70° C, V<sub>CC</sub> = AV<sub>CC</sub> = 5 ± 5%, V<sub>SS</sub> = AGND = 0V.

| Symbol Parameter  |                                    | Min | Тур  | Max | Units |  |

|-------------------|------------------------------------|-----|------|-----|-------|--|

| <u> </u>          | AV <sub>CC</sub> Operating Current |     | 15   | 21  | mA    |  |

| Alcc <sub>1</sub> | V <sub>CC</sub> Operating Current  |     | 5    | 6   | mA    |  |

| lcc <sub>1</sub>  | V <sub>BB</sub> Operating Current  |     | -15  | -21 | mA    |  |

| Alcc <sub>s</sub> | AV <sub>CC</sub> Standby Current   |     | 0.2  | 1   | mA    |  |

| Icc <sub>s</sub>  | V <sub>CC</sub> Standby Current    |     | 5    | 6   | mA    |  |

| Ibb <sub>s</sub>  | V <sub>BB</sub> Standby Current    |     | -0.6 | -2  | mA    |  |

| Pdo               | Operating Power Dissipation        |     | 175  | 250 | mW    |  |

| Pds               | Standby Power Dissipation          |     | 30   | 50  | mW    |  |

**DC CHARACTERISTICS** (Ta=0°C to 70°C, AV<sub>CC</sub> = V<sub>CC</sub> = 5V  $\pm$ 5%, V<sub>BB</sub> = 5V  $\pm$ 5%, AGND = V<sub>SS</sub> = 0V), supply voltage must be at the same potential as the 89C026XE power supply. Typical Values are for Ta = 25°C and nominal power supply values. V<sub>CC</sub>, and AV<sub>CC</sub>. V<sub>CC</sub>, AV<sub>CC</sub> and 89C026XE V<sub>REF</sub> must be nominally at the same potential.

Inputs: TX0, TX1, TX2, TX3, HYB, RST

Outputs: CLKOUT

| Symbol | Parameter             | Min                 | Max  | Units | Test Conditions             |

|--------|-----------------------|---------------------|------|-------|-----------------------------|

| lil    | Input Leakage Current | -10                 | + 10 | μА    | $V_{SS} \le Vin \le V_{CC}$ |

| Vil    | Input Low Voltage     | V <sub>SS</sub>     | 0.8  | ٧     |                             |

| Vih    | Input High Voltage    | 2.0                 | Vcc  | V     |                             |

| Vol    | Output Low Voltage    |                     | 0.4  | ٧     | lol ≥ -1.6mA,1 TTL load     |

| Voh    | Output High Voltage   | 2.4                 |      | V     | loh ≤ 50μa, 1 TTL load      |

| Vcol   | CLKOUT Low Voltage    |                     | 0.4  | V     | Load Capacitance = 60 pF    |

| Vcoh   | CLKOUT High Voltage   | 0.7 V <sub>CC</sub> |      | V     | Load Capacitance = 60 pF    |

### AC CHARACTERISTICS (Ta = 25°C, $V_{CC}$ = AV $_{CC}$ = 5V, $V_{SS}$ = AGND = 0V, $V_{BB}$ = -5V)

#### **ANALOG INPUTS: A02**

| Parameter                | Min | Тур | Max | Units | Test Condition      |

|--------------------------|-----|-----|-----|-------|---------------------|

| AO2 Receive Signal Level |     |     | -9  | dBm   | Hybrid Enabled      |

| AO2 Input Resistance     |     | 10  |     | MOhms | -2.5V < Vin < +2.5V |

| AO2 Allowed DC offset    | -30 |     | +30 | mV    | Relative to AGND    |

### **AUTO ZERO CAPACITANCE**

Capacitance =  $0.015 \mu F$ Tolerance =  $\pm 20\%$ Voltage Rating = 10V

Type = Non-Electrolytic, low leakage.

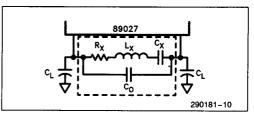

#### Figure 8. Crystal Equivalent Circuit

#### **CRYSTAL REQUIREMENTS**

| Parameter                     | Min      | Тур   | Max      | Unit | Comments             |

|-------------------------------|----------|-------|----------|------|----------------------|

| Frequency Accuracy (0°C-70°C) | -0.0035% | 12.96 | +0.0035% | MHz  | Refer to<br>Figure 8 |

| Rx                            |          | 10    | 16       | Ohms |                      |

| Cx                            |          | 0.024 |          | pF   |                      |

| Со                            | 5.1      | 5.6   | 6.1      | ρF   |                      |

| CL                            | -5%      | 33    | +5%      | pF   | 2 Load               |

|                               |          |       |          |      | Capacitors           |

Crystal Type: Parallel Resonant

### **ANALOG OUTPUTS: A01, AMP**

| Parameter                       | Min       | Тур                     | Max | Units                | C                        | omments                  |

|---------------------------------|-----------|-------------------------|-----|----------------------|--------------------------|--------------------------|

| Load Resistance<br>AO1<br>AMP   | 600<br>10 |                         |     | Ohms<br>kOhms        |                          | - The second of          |

| Load Capacitance<br>AMP         |           |                         | 100 | pF                   |                          | - 141                    |

| Audio Amp Gain<br>AO1 to Amp    |           | -9<br>-18<br>-26<br>-70 |     | dB<br>dB<br>dB<br>dB | Max<br>Mid<br>Min<br>Off | (Software Selectable)    |

| Audio Amp Gain(1)<br>AO2 to Amp |           | +12<br>+3<br>-4<br>-60  |     | dB<br>dB<br>dB<br>dB | Max<br>Mid<br>Min<br>Off | (Software<br>Selectable) |

#### NOTE:

<sup>1.</sup> Assumes on-chip hybrid is enabled. When on-chip hybrid is disabled, gain with respect to AO2 is reduced by 6 dB.

| Transmit Output Levei(1) |           |       |

|--------------------------|-----------|-------|

| TX 3,2,1,0               | Тур       | Units |

| 0000                     | +5        | dBm   |

| 0001                     | +4        | dBm   |

| •                        | •         | •     |

| •                        | •         | •     |

| •                        | •         | •     |

| 1110                     | -9        | dBm   |

| 1111                     | -9<br>-10 | dBm   |

- 1. For PSK and QAM transmit signal. For FSK transmit signal levels, they are typically 1 dB lower. All signals are measured at A01.

- 2. The tolerance for the above transmit levels are  $\pm\,1$  dBm.

## REFERENCE MANUAL

For reference purposes please refer to the Modem Reference Manual which contains a full description of the AT commands and S-registers supported by the 89C024XE Modern chip set.

#### **REVISION 003 HISTORY**

The following differences exist between Rev. -002 and this version of the data sheet:

- The MNP code for the 89C024XE has been revised to the 5.3 software. The major changes and improvements in 5.3 are listed below.

- Expanded NVRAM (9346) support which allows storage and retrieval of four phone numbers and two user profiles. Commands supported are &Zn, DS, &Wn and Zn.

- S11 DTMF duration and spacing register support.

- Factory defaults changed from &C0, &D0 to &C1, &D2 respectively.

- iv. The B command can select between V.21 and Bell 103 modes for 300 bps connections. The B/C pin on the 89C026XE is ignored.

- v. ATO from the call progress mode causes the modem to go into originate mode instead of answer mode. When off line, ATO gives "NO CARRIER" response, instead of going on line.

- vi. \S command is supported. This command displays the state of the most important modem configuration parameters on the terminal, 8 lines at a time.

- vii. If the modem is configured for both MNP and Synchronous modes of operation, then the modem will ignore the MNP parameters.

- viii. MR and CD LED drivers to write to Port 3, bits 2 and 3 are supported.

- ix. 600 bps operation is not supported.

More detail on these enhancements is provided in the modem reference manual.

- Receiver BER performance table has been expanded.

- Frequency and Phase jitter specs have been removed.

- 89024 reference manual has been superseded by the modem reference manual. This is a single manual for Intel's modem product line.